Immersion lithography is a technique used in semiconductor manufacturing to enhance the resolution and accuracy of the lithographic process. It involves using a liquid medium, typically water, between the lens and the wafer during exposure. By using a liquid with a higher refractive index than air, immersion lithography allows for smaller features to be created on the wafer.[1]

Immersion lithography replaces the usual air gap between the final lens and the wafer surface with a liquid medium that has a refractive index greater than one. The angular resolution is increased by a factor equal to the refractive index of the liquid. Current immersion lithography tools use highly purified water for this liquid, achieving feature sizes below 45 nanometers.[2]

Background

The ability to resolve features in optical lithography is directly related to the numerical aperture of the imaging equipment, the numerical aperture being the sine of the maximum refraction angle multiplied by the refractive index of the medium through which the light travels. The lenses in the highest resolution "dry" photolithography scanners focus light in a cone whose boundary is nearly parallel to the wafer surface. As it is impossible to increase resolution by further refraction, additional resolution is obtained by inserting an immersion medium with a higher index of refraction between the lens and the wafer. The blurriness is reduced by a factor equal to the refractive index of the medium. For example, for water immersion using ultraviolet light at 193 nm wavelength, the index of refraction is 1.44.[3]

The resolution enhancement from immersion lithography is about 30–40% depending on materials used. However,[clarification needed] the depth of focus, or tolerance in wafer topography flatness, is improved compared to the corresponding "dry" tool at the same resolution.[4]

The idea for immersion lithography was patented in 1984 by Takanashi et al.[5] It was also proposed by Taiwanese engineer Burn J. Lin and realized in the 1980s.[6] In 2004, IBM's director of silicon technology, Ghavam Shahidi, announced that IBM planned to commercialize lithography based on light filtered through water.[7]

Defects

Defect concerns, e.g., water left behind (watermarks) and loss of resist-water adhesion (air gap or bubbles), have led to considerations of using a topcoat layer directly on top of the photoresist.[8] This topcoat would serve as a barrier for chemical diffusion between the liquid medium and the photoresist. In addition, the interface between the liquid and the topcoat would be optimized for watermark reduction. At the same time, defects from topcoat use should be avoided.

As of 2005, Topcoats had been tuned for use as antireflection coatings, especially for hyper-NA (NA>1) cases.[9]

By 2008, defect counts on wafers printed by immersion lithography had reached zero level capability.[10]

Polarization impacts

As of 2000, Polarization effects due to high angles of interference in the photoresist were considered as features approach 40 nm.[11] Hence, illumination sources generally need to be azimuthally polarized to match the pole illumination for ideal line-space imaging.[12]

Throughput

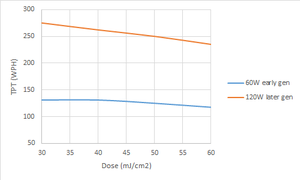

As of 1996, this was achieved through higher stage speeds,[13][14] which in turn, as of 2013 were allowed by higher power ArF laser pulse sources.[15] Specifically, the throughput is directly proportional to stage speed V, which is related to dose D and rectangular slit width S and slit intensity Iss (which is directly related to pulse power) by V=Iss*S/D. The slit height is the same as the field height. The slit width S, in turn, is limited by the number of pulses to make the dose (n), divided by the frequency of the laser pulses (f), at the maximum scan speed Vmax by S=Vmax*n/f.[13] At a fixed frequency f and pulse number n, the slit width will be proportional to the maximum stage speed. Hence, throughput at a given dose is improved by increasing maximum stage speed as well as increasing pulse power.

According to ASML s product information about twinscan-nxt1980di, immersion lithography tools currently[when?] boasted the highest throughputs (275 WPH) as targeted for high volume manufacturing.[16]

Multiple patterning

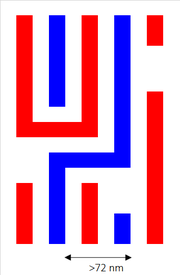

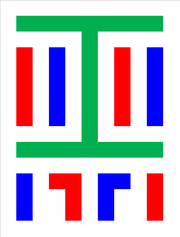

The resolution limit for a 1.35 NA immersion tool operating at 193 nm wavelength is 36 nm. Going beyond this limit to sub-20nm nodes requires multiple patterning.[17] At the 20nm foundry and memory nodes and beyond, double patterning and triple patterning are already being used[when?] with immersion lithography for the densest layers.

See also

References

- ^ Flagello, Donis (2004-01-01). "Benefits and limitations of immersion lithography". Journal of Micro/Nanolithography, MEMS, and MOEMS. 3 (1): 104. Bibcode:2004JMM&M...3..104M. doi:10.1117/1.1636768. ISSN 1932-5150.

- ^ "DailyTech - IDF09 Intel Demonstrates First 22nm Chips Discusses Die Shrink Roadmap". Archived from the original on 2010-08-28. Retrieved 2009-12-07.

- ^ Smith, Bruce W.; Kang, Hoyoung; Bourov, Anatoly; Cropanese, Frank; Fan, Yongfa (2003-06-26). "Water immersion optical lithography for 45-nm node". In Yen, Anthony (ed.). Optical Microlithography XVI. Vol. 5040. SPIE. pp. 679–689. Bibcode:2003SPIE.5040..679S. doi:10.1117/12.485489.

- ^ B. J. Lin, J. Microlith Microfab. Microsyst. 1, 7 (2002).

- ^ A. Takanashi, T. Harada, M. Akeyama, Y. Kondo, T. Karosaki, S. Kuniyoshi, S. Hosaka, and Y. Kawamura, U. S. Patent No. 4,480,910 (1984)

- ^ Burn J. Lin (1987). "The future of subhalf-micrometer optical lithography". Microelectronic Engineering 6, 31–51

- ^ "A Whole New World of Chips". Business Week. Archived from the original on 2011-02-21.

- ^ Y. Wei and R. L. Brainard, Advanced Processes for 193-nm Immersion Lithography, (c) SPIE 2009, Ch.6.

- ^ J. C. Jung et al., Proc. SPIE 5753 (2005).

- ^ B. Rathsack et al., Proc. SPIE 6924, 69244W (2008).

- ^ C. Wagner et al., Proc. SPIE vol. 4000, pp. 344-357 (2000).

- ^ B. W. Smith, L. V. Zavyalova, and A. Estroff, Proc. SPIE 5377 (2004).

- ^ a b "M. A. van den Brink et al., Proc. SPIE 2726, 734 (1996)" (PDF). Archived from the original (PDF) on 2017-08-09. Retrieved 2018-07-16.

- ^ I. Bouchoms et al., Proc. SPIE 8326, 83260L (2012)

- ^ Inc, Rostislav Rokitski, R. Rafac, R. Dubi, J. Thornes, J. melchior, T. Cacouris, M. Haviland and D. Brown, Cymer (2013). "120-W ArFi Laser Makes Higher-Dose Lithography Possible". www.photonics.com. Retrieved 2022-11-09.

{{cite web}}:|last=has generic name (help)CS1 maint: multiple names: authors list (link) - ^ "The ASML NXT:1980Di lithography system". www.asml.com. nd. Retrieved 2022-11-09.

- ^ Haley, G. (2023). 193i Lithography Takes Center Stage...Again. Semiconductor Engineering. Retrieved from https://semiengineering.com/193i-lithography-takes-center-stage-again